# Table of contents

| 1. | I <sup>2</sup> C | protocol                                                                                      | 2 |

|----|------------------|-----------------------------------------------------------------------------------------------|---|

|    | 1.1.             | General description                                                                           | 2 |

|    | 1.2.             | Communication phases                                                                          | 3 |

|    | 1.3.             | I <sup>2</sup> C communication overview                                                       | 4 |

|    |                  |                                                                                               |   |

| 2. | Dig              | gital data transfer on I <sup>2</sup> C bus                                                   | 4 |

|    |                  | gital data transfer on I <sup>2</sup> C bus<br>Pressure data transfer on I <sup>2</sup> C bus |   |

|    | 2.1.             |                                                                                               | 4 |

|    | 2.1.<br>2.2.     | Pressure data transfer on I <sup>2</sup> C bus                                                | 4 |

The technical data may be altered without prior notice

# 1. I<sup>2</sup>C protocol

### 1.1. General description

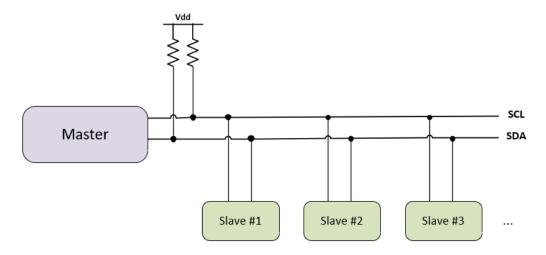

In I<sup>2</sup>C communication a serial data line (SDA) and a serial clock line (SCL) are required for the communication between the connected devices to I<sup>2</sup>C bus. Both connected lines SDA and SCL are bidirectional, which are connected to the supply voltage with pull-up resistors (see application circuit on **Figure 1**).

As seen on **Figure 1** there can be more slave devices (up to 127) connected to I<sup>2</sup>C bus, which is limited to 7 bit slave address. I<sup>2</sup>C bus is free when both connection lines are HIGH and can be set to LOW by the devices which are connected to the I<sup>2</sup>C bus.

Figure 1. I<sup>2</sup>C communication example

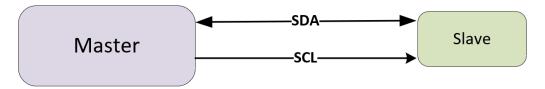

$I^2C$  communication acts as a Master – Slave principle (see **Figure 2**), there is a master device which generates the clock (SCL) and also generates START & STOP command for data transition.

Figure 2. Master-Slave principle

Masters and slaves can act as transmitter or receiver depending on the information, if that needs to be sent or read. Transmitter is the device which sends data to the I<sup>2</sup>C bus ("master transmitter" normally sends requests to the slave and the "slave transmitter" normally sends information replies to the master). The receiver is the device which receives data from I<sup>2</sup>C bus.

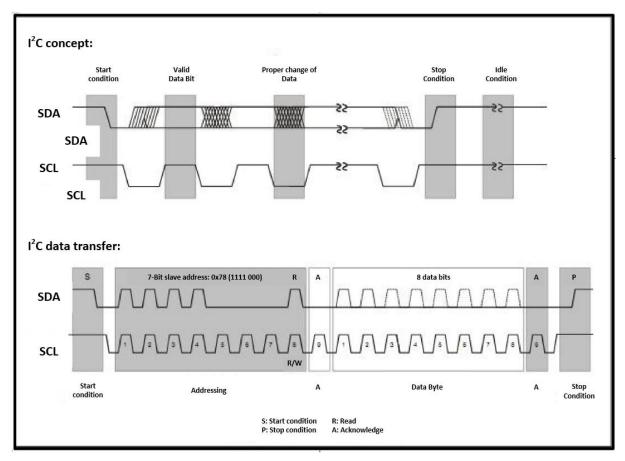

I<sup>2</sup>C standard protocol is showed in **Figure 3**.

Figure 3. I2C Standard communication protocol

#### 1.2. Communication phases

- Buss free Idle state: When the bus is free both lines SCL and SDA are pulled up HIGH.

- START condition (S): Each data transfer starts with the start condition, which is always sent by the master. This start condition acts as a signal to all I<sup>2</sup>C connected devices giving information that there will be something transmitted. The start condition is defined as a transition from HIGH to LOW on the SDA line when the SCL line is HIGH (see Figure 3).

- **STOP condition (P)**: Each data transfer stops with the stop condition, which is also generated by the master when a data transfer has finished. Stop condition is defined as a transition from LOW to HIGH on the SDA line when the SCL line is HIGH (see **Figure 3**).

- Valid data: Data is always transmitted in bytes (8 bits) starting with the MSB (most significant bit). One data bit is transferred with each clock pulse. Transmitted data are valid (after generating start condition) only during HIGH period of clock and data changes can be done during LOW period of clock (see Figure 3).

- Acknowledge (A): Each sent byte needs to be followed with the acknowledge bit generated from the receiver that correct data has been received. Acknowledge means also that device can continue with further data transfer. For that purpose, the master must generate extra clock pulse. The transmitter releases clock HIGH during acknowledge clock pulse, if not then further bytes will not be sent.

- Slave address: After the start condition, the master sends the addressing byte slave address to define with which slave device he wants to communicate. This addressing byte includes 7-bit slave address (up to 128 devices) + 1 R/W bit (data direction bit). If R/W bit is set to "0" (W) then master wishes to transmit data to the selected slave. If R/W bit is set to "1" (R) then the

**Huba Control**

master request data from the slave. The addressed slave answers with an acknowledge, all other slaves connected to the I<sup>2</sup>C-bus ignore this communication.

HUBA CONTROL Type 450 pressure sensor have a default slave address programmed to 0x28 (0101 000b). For connecting more slave devices to I<sup>2</sup>C bus each connected device should have its own slave address (up to 128 devices).

#### 1.3. I<sup>2</sup>C communication overview

**Figure 3** shows a complete data transfer. After generating the start condition, the master also sends the slave address with data direction bit (R/W), which gives read or write transfer. The addressed slave replies to this request always with the acknowledge (A) first. Now, unlimited numbers of data (bytes) can be transferred, which needs to be always confirmed with the acknowledge bit. This transfer can be stopped by the master by generating the stop condition. If master wishes to communicate also with another slave address, then can generate a second start condition without stopping the first one.

# 2. Digital data transfer on I<sup>2</sup>C bus

### 2.1. Pressure data transfer on I<sup>2</sup>C bus

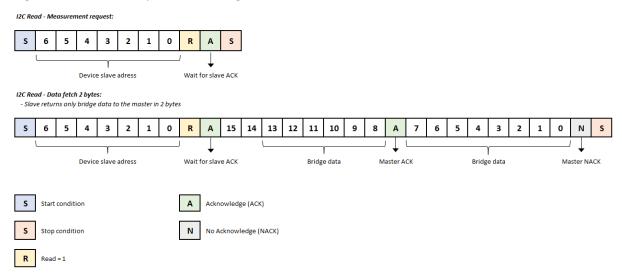

Digital data transfer is presented in Figure 4

Figure 4. Digital pressure data transfer from HUBA Type 450 sensor

Pressure output signal from HUBA CONTROL Type 450 come as 14-bit values to the output register. Master, which would like to read this data, starts communication with the start condition. After that, the master sends 7-bit slave address (factory default is 0x28) and data direction bit R (R = "1"). The slave confirms this address with the acknowledge (A) bit first and afterwards sends the desired data with 2 bytes: 6 bits [13:8] of first byte is the most significant byte for pressure value, second byte [7:0] is the least significant for pressure value. The master must confirm each received byte with the acknowledge bit (see Figure 4). Master can stop the data transfer by sending the stop condition or can generate additional acknowledge bit after 2 receiving bytes of data (pressure) for continuing data receiving from slave (type 450 sensor).

### 2.2. Calculation pressure formula

Master receives pressure data as a 14-bit values which can be converted to actual pressure data with pressure units in mbar using the simple formula below.

### Definitions:

- p = pressure (mbar)

- p<sub>min</sub> = min pressure (mbar)

- $p_{max}$  = max pressure (mbar)

- D = digital pressure (counts)

- D<sub>max</sub> = max digital pressure (counts)

- D<sub>min</sub> = min digital pressure (counts)

- S = sensitivity (count/mbar)

$$S = \frac{D_{max} - D_{min}}{p_{max} - p_{min}}$$

Equation 1.

$$p = \frac{D - D_{min}}{S} + p_{min}$$

Equation 2.

Example: for our pressure sensor with pressure range 0 to 3 mbar with analogue output 0.5 to 4.5 V (equivalent digital output 1638 to 14745 counts), a digital value of 7850 counts is measured. Let's calculate this value in pressure units mbar:

$$S = \frac{14745 - 1638}{3 \; mbar - 0 \; mbar} = 4369 \; counts/mbar$$

Equation 3.

$$S = \frac{7850 - 1638}{4369} + 0 \, mbar = 1,42 \, mbar$$

Equation 4.

## 2.3. I<sup>2</sup>C Timings parameters

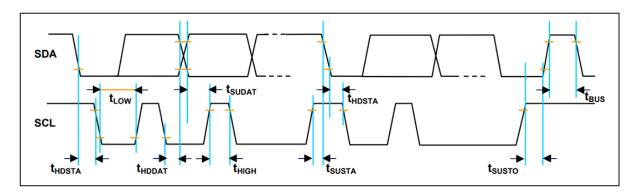

Figure 5. Timings parameters

| PARAMETER                                                              | SYMBOL             | MIN |     | UNITS |

|------------------------------------------------------------------------|--------------------|-----|-----|-------|

| SCL clock frequency                                                    | f <sub>SCL</sub>   |     | 100 | kHz   |

| Start condition hold time relative to SCL edge                         | t <sub>HDSTA</sub> | 0.1 |     | μs    |

| Minimum SCL clock low width 1)                                         | t <sub>LOW</sub>   | 0.6 |     | μs    |

| Minimum SCL clock high width 1)                                        | t <sub>HIGH</sub>  | 0.6 |     | μs    |

| Start condition setup time relative to SCL edge                        | t <sub>SUSTA</sub> | 0.1 |     | μs    |

| Data hold time on SDA relative to SCL edge                             | t <sub>HDDAT</sub> | 0   |     | μs    |

| Data setup time on SDA relative to SCL edge                            | t <sub>SUDAT</sub> | 0.1 |     | μs    |

| Stop condition setup time on SCL                                       | t <sub>susto</sub> | 0.1 |     | μs    |

| Bus free time between stop condition and start condition               | t <sub>BUS</sub>   | 2   |     | μѕ    |

| Combined low and high widths must equal or exceed minimum SCLK period. |                    |     |     |       |

Figure 6. Timing I<sup>2</sup>C protocol